by Zsolt

Kerekes, editor - StorageSearch.com

SSD

Controllers and IP define the personality of the SSD

Controller architecture and effective implementation processes

transform unreliable me-too

memory chips into the

diverse range of application optimized (or not) SSDs which you can see in the

market today.

SSD news

processors in

SSDs

SSD

reliability - articles

SSD

interface glue chips and IP

SSD endurance myths

and legends

how

fast can your SSD run backwards?

some thoughts about SSD

customization

Why size matters in

SSD design architecture

Adaptive R/W

and DSP ECC IP for flash SSDs

do

3d nand layers enable big architecture in small chipsets?

are we ready for

infinitely faster RAM? (and what would it be worth)

how the market came to

care so deeply about the identity of SSD controllers (classic article)

|

| . |

| SSD

controller news (extracted from SSD

news) |

Silicon Motion ships >

750 million NAND controllers / year

Editor:- October 5, 2018 - Silicon Motion

says "We ship over 750 million NAND controllers annually and have shipped

over 5 billion NAND controllers in the last 10 years, more than any other

company in the world."

They might have been saying that for some

while but I only noticed it today when looking in the footnotes of their

Q3 2018

preliminary press release which warned that "revenue is expected to be

within the lower half of the original guidance range of $136.0 million to $142.9

million that the company issued on August 1, 2018." (Maybe that's what

happens if markets adjust to a smaller supply of more expensive than anticipated

memory chips - we'll have to wait to see Si Motion's analysis on October

30, 2018.)

Editor's comments:- the shipment numbers for controllers

show how large the SSD market has become.

new thinking in SSD controller techniques reveals "layer

aware" properties exploitable in 3D nand flash

Editor:-

August 28, 2018 - A new twist using

RAID ideas in

SSD controllers has

surfaced recently in a research paper -

Improving

3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process

Variation (pdf) by Yixin Luo and Saugata Ghose (Carnegie Mellon

University), Yu Cai (SK Hynix), Erich F. Haratsch (Seagate Technology) and

Onur Mutlu (ETH Zürich) - which was presented at the SIGMETRICS

conference in June 2018.

The authors say that in tall 3D nand (30 layers and upwards) the raw

error rate in blocks in the middle layers are significantly worse (6x) compared

to the top layer. Therefore to enable more

reliable and

faster SSDs using 3D nand for enterprise applications they propose a new type

of RAID which pairs together the best predicted half of a RAID word with the

worst predicted half from another chip in the same SSD.

This new RAID

concept starts to be feasible in a very small population of chips - unlike

traditional 2D nand schemes which need more chips to be installed in the SSD.

The

new RAID is called Layer-Interleaved RAID (LI-RAID) - which the authors

say "improves reliability by changing how pages are grouped under the RAID

error recovery technique. LI-RAID uses information about layer-to-layer process

variation to reduce the likelihood that the RAID recovery of a group could fail

significantly earlier during the flash lifetime than the recovery of other

groups." ...

read the article (pdf)

Editor's comments:- the new RAID is

just one of many gems in this research paper. Others being the discovery that

remanence in 3D nand includes a significant short term charge loss (in the first

few minutes after writes), and also that an endurance based characterization of

a small part of each chip can be used to predict an optimized layer dependent

threshold read voltage for all the layers in the chip. I've discussed the

significance of adding the concept of "layers" to "number of raw

chips" to the thinking in SSD controller design in my recent

home

page blog.

doing useful stuff with ReRAM and a MIL TLC?

Editor:-

May 31, 2018 - Some SSD design related stories in the

SSD news archive for

May 2018 include:-

- ReRAM AI accelerator chip

- Memory makers being sued for price fixing

- Burlywood claims TrueFlash will save 40% of flash cost

- QLC is going into cloud SSDs (yawn) - TLC is going into avionics

(respect)

testing SSD safety, uprating MRAM, Google Workloads

Editor:-

April 30, 2018 - Some SSD design related stories in the

SSD news archive

for April 2018 include:-

- new improved MRAM cell design promises better retention

- study shows processing in memory can save power at the same time as

speeding applications up

- customer qualifications for critical SSDs on trains take longer than

designing the original SSD

SandForce cofounder says why his new company is designing cloud

chips

Editor:- March 10, 2018 - "In any computer architecture,

it takes a lot more energy to fetch and schedule an instruction than it does to

execute that instruction" says Rado Danilak,

founder and CEO - Tachyum

- in his new blog -

Moore's

Law Is Dying - So Where Are Its Heirs? - which among other things - shows

how the transactional costs of fetching instructions and data in classical

processors. ...read

the article

Editor's comments:- the needs of the cloud, coupled

with growing understanding between the tradeoffs between

processors,

memory,

controller

dynamics, software

and energy consumption since the widespread deployment of solid state storage

have been the inspiration for rethinking all the classical elements of computer

architecture. Some of that thinking has been rooted in the memory space but

just as significant has been a rethinking of what processors should aim to do.

Tachyum announced external funding for its Cloud Chip

last month. And

as with previous disruptive technologies - part of the warm up process for the

market - is to educate more people about how things work now so they can better

appreciate what the new technologies offer.

NGD Systems announces Series B funding

Editor:-

February 13, 2018 - NGD

Systems today

announced

the completion of Series B round of financing with $12.4 million.

The

proceeds will be used for strategic growth initiatives, including the

acceleration of go-to-market activities, continued innovation of the company's

technology, and migration of its advanced 14nm SSD controller to mass

production.

SLC / MLC / TLC - tactical / permanent / real / virtual?

tradeoffs

in the design of mixed flash hybrid SSDs

Editor:- December 20,

2017 - This month I received a copy of a new (to me) paper -

a Survey

of Techniques for Architecting SLC/MLC/TLC Hybrid Flash Memory based SSDs (27

pages pdf) - from Sparsh Mittal,

Assistant Professor at Indian Institute of

Technology Hyderabad who is among the co-authors of this significant

reference document.

Re the scope - the authors say "For sake of a

concise presentation, we limit the scope of this paper as follows. We focus on

software-level management techniques for hybrid SSDs and not their circuit-level

design issues. We include techniques which use at least two types of Flash and

not those that merely use an SCM with a Flash cell-type.We focus on the key

ideas of each work and include only selected quantitative results, since

different works use disparate evaluation platforms and workloads. We hope that

this paper will be useful for computer architects, SSD designers and researchers

in the area of storage architectures."

Among other things the

paper discusses a wide range of externally referenced techniques including:-

- tradeoffs in using some portion of TLC or MLC as virtual SLC (to improve

latency and endurance)

- reliability and performance tradeoffs using volatile versus non volatile

RAM in buffers

- revitalizing worn MLC blocks as SLC

- varying the size of SLC designated buffers based on analyzing application

usage to optimize garbage collection

The authors note various

factors which are changing or need to change compared to previous generations

of SSD design.

- better runtime adaptation of control parameters

- the need for hybrid SSD specific simulators

- fairness and QoS (quality of service) joining the formula of design goals

in SSD design in addition to the traditional must-haves of performance and

reliability

If you've ever wondered about how to optimize SSD design by

using a mix of flash memory types in the same SSD then this paper is an

invaluable reference guide to the techniques which have been written about in

the public domain. ...read the

article (pdf)

IntelliProp demonstrates Gen-Z memory controller

Editor:-

November 13, 2017 - IntelliProp

today

announced

demonstrations of 2 new controller IPs.

- A memory controller for the emerging Gen-Z memory interface.

IntelliProp's

Gen-Z IPA-PM185-CT "COBRA" controller combines DRAM and NAND and

sits on the Gen-Z fabric, not the memory bus. COBRA has the ability to support

byte addressability to DRAM cache and Block addressability to NAND flash.

COBRA-based Gen-Z memory modules provide low latency, persistent, shared memory

access to multiple processors and accelerators on the Gen-Z fabric supporting up

to 32GB of DRAM and 3TB of NAND.

- An NVMe 1.3 compatible host accelerator IP core.

IntelliProp's

IPC-NV164-HI for for Xilinx and Altera FPGAs accelerates performance by

off-loading command and completion queue management from the processor to

hardware.

Series A funding for RISC CPUs in DRAM

Editor:-

September 8, 2017 -

UPMEM - a fabless semiconductor

startup - today announced

3 million Euros series A funding for its Processing In-Memory technology.

This

integrates user-API accessible RISC processors as SoCs in DRAM. The company has

been

reported

in eeNews (Oct 2016) as saying...

"The fundamental benefit of

processing-in-memory is the combination of DRAM and CPU. We attach 1 DPU per

DRAM bank. It means 16 cores per 8Gbit DRAM chip. On a 16Gbyte DIMM, we deliver

256 cores, and 8 of them can be added to a standard CPU socket. We end up with a

co-processing system of 2048 cores together with 128Gbytes of DRAM per socket."

The PIM chip, integrating UPMEM's proprietary RISC processors (DRAM

Processing Units, DPUs) and main memory (DRAM), is the building block of the

first efficient, scalable and programmable acceleration solution for big data

applications. Associated with its Software Development Kit, the UPMEM PIM

solution can accelerate data-intensive applications in the datacenter servers 20

times, with close to zero additional energy premium.

"We are no

longer in an era were CPUs and other hardware getting continuously faster would

mask the slow speed of inefficient software," said Reza Malekzadeh, General

Partner at Partech Ventures (among the investors). "UPMEM's solution

addresses the performance needs of modern scale-out applications while

preserving datacenter and infrastructure hardware investments."

Nimbus enters the SSD controller market

Editor:-

August 10, 2017 - Nimbus

Data Systems recently

announced

it has entered the SSD

controller market with a reference design for high capacity

SAS SSDs.

Editor's

comments:- this move is part of a strategic trend in the market. For more see my

new blog - sauce

for the SSD box gander

Mobiveil releases FPGA controller for 16 lane 16G NVMe SSDs

Editor:-

August 3, 2017 -

Mobiveil today

announced

availability of its FPGA-based SSD development platform targeting the latest

3D NAND devices. Error correction is performed using ether BCH or LDPC.

The

NVMe (rev 1.3 compatible) controller supports a multi-port configuration for

efficient I/O virtualization and multi-path I/O and namespace sharing.

Mobiveil's silicon-proven PCIe solution has added Gen4 support for up

to 16 lanes at 16G line rate with availability of 512 bit Data path user

interface. The PCIe controller offers AXI4 interface and DMA capabilities for

seamless integration into an ARM Advanced Microcontroller Bus Architecture SoC

implementation.

ReRAM in the CPU

Editor:- June 7, 2017 - These are

some of the ideas which emerge from a slideshare -

Rethink

with ReRAM by Crossbar

from a presentation at the recent

Memory+ Conference.

- Standard memory busses are too slow to support the computational needs

of new distributed (and always on) AI applications which leverage IoT.

- The only way to improve ultimate "time to get answers"

performance is to integrate storage on the same die as the processor.

- ReRAM can be embedded in SoCs in any CMOS fab to deliver battery

friendly latency under 5nS.

new patents for Corsair and Violin

Editor:- May 18,

2017 - News about the issuance of new patents in the SSD and memory market this

month include:-

- Corsair -

9,645,619

- described by its inventor Bobby Kinstle Senior

Project Manager in this way. "This one is for using tiny heat pipes to

remove heat from memory devices in really tight spaces."

- Violin

(now under new ownership) announced 2 new patents.

9,495,110

- technology behind the company's 4-way active-active RAID controllers. "Method

for managing storage memory resources for LUN allocation and related maintenance

operations within a system of high-availability distributed RAID controllers,

while maintaining coherency and high input/output speed."

9,547,588

- "Method for managing the compression and/or encoding of digital data

being stored in non-volatile memory, such as flash memory, to improve the

performance of the solid state memory cells with respect to program/erase

operations. This method may reduce power consumption and storage space usage,

while enhancing the wear lifetime characteristics of the memory media."

now Cinderella industrial systems with "no-CPU"

budgets and light wattage footprints can go to the NVMe speed-dating ball

Editor:-

April 19, 2017 - A dilemma for designers of embedded systems which require high

SSD performance is how can you get the benefits of enterprise class NVMe SSDs

for simple applications - which integrate video for example - without at the

same time escalating the wattage footprint of the entire attached micro server?

A

new paper published today by IP-Maker -

Allowing

server-class storage in embedded applications (pdf) discusses the problem

and how their new FPGA based IP enables any NVMe PCIe SSD to be used in

embedded systems to provide sub-microsecond latency using "20x better power

efficiency, and 20x lower cost compared to a CPU-based system."

The

company says the NVMe host IP - which is now available - can be used in an FPGA

connected between the PCIe root port and the cache memory, internal SRAM or

external DRAM. It fully controls the NVMe protocol by setting and managing the

NVMe commands. No CPU is required. It supports PCIe gen 3 x 8 interface.

Michael Guyard, Marketing

Director said that - among other things - applications include:-

- military recorders

- portable medical imaging

- mobile vision products - in robots and drones

...read the

article (pdf)

Editor's comments:- Now Cinderella

embedded systems with low cost budgets and low wattage footprints can go to the

enterprise NVMe performance ball. The new magic - in the form of the FPGA IP

released today by IP Maker - has the potential to transform the demographics

and class of SSDs seen in future industrial systems.

See also:-

optimizing

CPUs for use with SSDs, SSD

glue chips

Liqid named among fastest growing storage companies

Editor:-

March 25, 2017 - Liqid

was named among the 10 listed in a new article -

10

Fastest Growing Storage Companies 2017 - by Silicon Review .

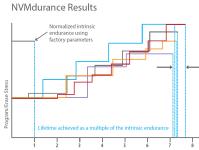

NVMdurance awarded US patent for Adaptive Flash Tuning

Editor:-

March 21, 2017 - NVMdurance

today

announced

that it has been granted US patent 9,569,120 for Adaptive Flash Tuning.

CNEX Labs has amassed $60 million for new SSD controller

Editor:-

March 15, 2017 - CNEX Labs

today announced its

Series C round of financing which brings total funding to date over $60

million. The company will use the funding for mass production and system

integration for lead customers of its NVMe-compliant SSD controllers for

hyperscale markets. The new controllers will enable full host control over

data placement, I/O scheduling, and other application-specific optimizations, in

both kernel and user space.

See also:-

adaptive

intelligence flow symmetry (1 of 11 Key Symmetries in SSD design).

Micron chooses Hyperstone's USB controller for reliable IoT SSDs

Editor:-

March 6, 2017 -

Hyperstone's

U9 - USB 3.1 flash Memory controller has been integrated into Micron's new eU500- a

USB SSD aimed at the

industrial IoT

and telco market.

The eU500 has sequential read/write speed of up to

170/120 MB/s and a steady state 4K random read/write performance of 3,000/1,000

IOPS.

controllernomics - joins the memory latency to do list

Editor:-

February 20, 2017 - As predicted 8 years ago - the widespread adoption of SSDs

signed the death warrant for hardware

RAID controllers.

Sleight

of hand tricks which seemed impressive enough to make hard drive arrays (RAID) seem fast in the

1980s - when viewed in slow motion from an impatient SSD perspective - were

just too inelegant and painfully slow to be of much use in true

new dynasty

SSD designs.

The confidence of "SSDs everywhere"

means that the data processing market is marching swiftly on - without much

pause for reflection - towards memory centric technologies. And many old

ideas which seemed to make sense in 1990s architecture are failing new tests

of questioning sanity.

For example - is

DRAM the fastest main

memory? No -

not when the capacity needed doesn't fit into a small enough space.

When

the first solutions of "flash as RAM" appeared in

PCIe SSDs many years

ago - their scope of interest was software compatibility. Now we have solutions

appearing in DIMMS in the memory channel.

This is a context where

software compatibility and memory latency aren't the only concerns. It's

understanding the interference effects of all those other pesky controllers in

the memory space.

That was one of the interesting things which emerged

in a recent conversation I had with Diablo Technologies

about their Memory1. See what I learned in the blog -

controllernomics

and user risk reward with big memory "flash as RAM"

Fujitsu says in-memory dedupe before writes to flash can double

best write speed

Editor:-

December 5, 2016 - Fujitsu

today

announced

the development of a high-speed in-memory data deduplication technology for

use in all-flash arrays. The method decides if there is enough time to

search for duplicates in the flash array while retaining the data in cache

(low load condition). If so then writes to the flash array are only performed

after dedupe. Fujitsu says that for some workloads where there are many

duplications such as virtual desktops this can improve the user experience.

Mobiveil's Universal NOR Controller Allows SoC Designers to

Leverage Adesto's EcoXiP Flash Memory

Editor:-

November 30, 2016 - Mobiveil

today

announced

it is working with Adesto Technologies

to enhance the memory in low capacity intelligent IoT systems.

Incorporating Mobiveils U-NFC controller to control the new Adesto

EcoXiP flash will

provide SoC designers an eXecute-in-Place solution that more than doubles the

performance of alternative approaches using standalone NOR-Flash memory.

Silicon Motion has SD 5.1 flash controller for Android market

Editor:-

November 21, 2016 - Silicon Motion

today announced

the "world's first merchant SD 5.1 controller solution."

"Android

Smartphone shipments accounted for more than 85% of the worldwide market share,

and 70% to 80% of these phones have microSD slots," said Nelson Duann,

Senior VP of Product Marketing at Silicon Motion, "With the

SM2703

controller (2000 / 650 random R/W IOPS on a single TLC die) now supporting

SD 5.1, our partners can rapidly bring to market a new generation of SD cards to

enable a much better user experience and extend the usability of the Android

smartphones."

See also:-

SSD controllers,

storage market research

patent in China for NVMdurance's flash software

Editor:-

August 31, 2016 - NVMdurance

today

announced it has been

granted a patent in China related to its endurance optimization software.

There

are several aspects to the company's multi-stage lifecycle endurance

management.

During

the memory characterization and design phase its Pathfinder software

determines multiple

sets of viable flash register values, using a custom-built suite of

machine-learning techniques. During

the memory characterization and design phase its Pathfinder software

determines multiple

sets of viable flash register values, using a custom-built suite of

machine-learning techniques.

Then in production, controllers which

use its Navigator firmware choose which of these predetermined sets to use for

each stage of life to ensure that the flash lasts as long as possible.

new memories? new security risks?

Editor:- August 4,

2016 - Is remanence a security risk in persistent memory? That's the topic of

my new blog

here on

StorageSearch.com

If

you aren't yet ready to evaluate these new SCM style NVDIMMs you might think

you can skip this article.

That's OK as long as you already were aware

that that data recovery

has always been feasible in old style

DRAM too. ...read the

article

IP-Maker releases Gen 3 NVMe PCIe reference design

Editor:-

July 11, 2016 - for designers of

PCIe SSDs - IP-Maker has released

its new Gen 3 NVMe PCIe reference design which is based on the VC709

evaluation kit by Xilinx.

It's

integrated with Xilinx's

Virtex-7

PCIe Gen3 hard IP and a soft DDR3 controller. The

UNH-IOL

NVMe compliant design uses

a x4 lanes configuration.

DIMM wars at battery scale - FLC from Marvell

Editor:-

May 12, 2016 - When thinking about

SSD / SCM DIMM

wars - most of the buzz in the past year has been focused on the impacts of

replacing DRAM with

flash at the

enterprise

server and cloud

levels. But the same concepts can be applied (albeit with different

efficiency gains) at

the implementation level of battery powered embedded devices and wearables.

In

a recent blog -

How

Marvell FLC Redefines Main Memory - by Hunglin Hsu, VP

- Marvell

provides authoritative examples of the replacement ratios possible in a phone

design.

A strategic lesson to guide future designers is that even

while getting a 50% power consumption reduction (due to flash as RAM) it

is also feasible to increase application performance at the same time because

the software can work with a larger memory capacity (due to the lower

cost of flash

bytes).

Among other things Hunglin says - "With FLC, better

performance can be achieved by reporting to the operating system a larger than

physically implemented main memory. The operating system is thus less likely to

kill background apps, which is why the fast app switching is possible. The FLC

hardware does all the heavy lifting in the background and frees up the tasks of

the operating system." ...read

the article

data noise reduction techniques in nvm

Editor:- April

22, 2016 - A recently published book -

Channel Coding

Methods for Non-Volatile Memories (145 pages, $130) cowritten by Lara Dolecek

and Frederic Sala

University of California, provides an overview of recent developments in

coding for nvms, and, by presenting numerous potential research directions, may

inspire other researchers to contribute to this timely and thriving discipline.

Editor's

comments:- this appears to be focused on the DSP and ECC end of the

Adaptive R/W

flash care management & DSP IP revolution which during the last 4 years

or so has been changing the way that new

memory technologies with

poor intrinsic data integrity (high noisiness - when viewed from a classical

ECC data angle) can be upcycled to construct higher quality, more reliable

solid state storage by adaptive and interventionist coding strategies.

2 ASIC roles for PCIe based BiTMICRO SSD controllers

Editor:-

March 25 , 2016 - 5

years ago when BiTMICRO

unveiled an earlier generation of its high performance enterprise SSD

controller architecture - it was clear that their preference was for a chipset

which included 2 different types of functionality.

This kind of

thinking wasn't unique at that time - as I'd seen similar things in

rackmount SSD

designs before but (unlike BiTMICRO) those other designs were captive and not

offered as COTS SSD

controllers.

How many controller chips do you really need for a

PCIe SSD?

In

a new blog

today BiTMICRO explains why its current generation of controllers continues

using a 2 ASIC architecture with one acting as a flash array extender and the

other as the main PCIe host interface controller.

Among other things

the blog says "To increase flash channel bandwidth and capacity, more flash

channel expander chips can be instantiated and connected to the main controller."

As noted in the SSD

design heresies - SSD vendors often have different implementation

architecture approaches which compete in similar application slots. When

evaluating different types of offerings it can be useful to ask yourself - which

direction is my own design likely to stretch in future? (Towards more

performance? lower cost? bigger scale? adjacent application role? etc.)

BiTMICRO's blog clarifies where they see their strengths in the market. ...read the

article

Hyperstone samples new industrial USB SSD controller

Editor:-

February 15, 2016 - Hyperstone

is sampling a new USB 3.1 Flash memory controller - the

U9

- in a TFBGA-124 package - for industrial applications.

Among other

things the ECC engine can correct up to 96-Bit/1KB. Power management features

include automatic power-down during wait periods for host data or flash memory

operation completion and automatic sleep mode during host inactivity periods.

Editor's

comments:- As you'd expect from a

USB device it's not

intended for heavy write applications - and although some of the data integrity

features are suggested to be enterprise compatible - the sustained random write

speed for 4KB is 5MB/s (30x slower than the peak sequential write.)

Nevertheless

- given the portability of strategic applications and system software between

form factors and the convenience of

DWPD as a way of grouping

SSDs for different roles I asked Hyperstone if they can supply an indicative

range of DWPD for the new USB controller (when used with various classes of

memory and DRAM size). I got this answer from Axel Mehnert VP

Marketing who said this.

"Yes, we can give you such ratings

Hyperstone has a web based lifetime estimation tool which can be accessed by

registered users of our site. There you can play with several settings and

Flash configurations in order to get DWPD data also correlating to several

different access patterns."

new SSD Bookmarks by Cadence

Editor:- February 5,

2016 - You all know Cadence

right?

So what set of online resources do you think they'd recommend

to newcomers who want to learn more about SSDs? (BTW - Rules of this game

disallow mouse links in the mix.)

You don't have to guess. I asked.

And you can see

Cadence's

suggested SSD Bookmarks today in the

new series

on StorageSearch.com

Marvell is first to ship Host Memory Buffer feature in NVMe SSD

controller

Editor:- January 5, 2016 - Marvell today

announced

expansion of its NVMe SSD controller technology to support Host Memory Buffer

(HMB), an NVMe revision 1.2 feature enabling DRAM-less (skinny) flash

SSDs to use host memory and achieve performance comparable to SSD designs with

regular embedded DRAM but

at much lower cost and power consumption.

3 new educational flash blogs

Editor:- December 11,

2015 - Here are some flash SSD blogs I've seen this week which are aimed

at educating SSD specifiers in embedded markets.

- Soft-Decoding

in LDPC based SSD Controllers - from PMC-Sierra -

includes clear explanations about some of the read again (re-read) recovery

strategies which can be used as part of the tool set in

adaptive R/W

and DSP ECC when things go wrong.

For example - "Read the

same section as the original hard data but use a different set of read threshold

voltages inside the NAND."

These techniques are rarely shared

publicly in such detail and are real life optimizations unlike the imaginary

techniques I discussed in my 2011 fictional company profile of

XLC Disk

- SSD

101 - Everything You Ever Wanted to Know - aimed at newcomers to the

concepts and jargon in

industrial SSDs

is a new framework overview from Cactus Technologies

which links together a bunch of their earlier short blogs. These articles

include good diagrams of flash planes, controllers and cells.

Re the

title "SSD 101 etc" - how far it satisfies "everything"

you want to know is debatable. But if you're starting out in flash and need the

reassurance that the technology background is sound - this series is better

than many others I've seen.

Processors in SSD controller design - a new series

Editor:-

October 12, 2015 - Coming soon on the mouse site - a new series...

aspects of

SSD design - processors used in SSDs. This is for those of you who

know in your bones that to get the SSD you want - you need to design your

own controller.

Datalight's SSD firmware to go into manned spacecraft

Editor:-

September 17, 2015 - Datalight

today announced that its embedded filesystem (Reliance

Nitro) and FTL (FlashFX

Tera) have been selected by NASA for use

onboard future manned spacecraft being developed as part of the

Orion

program.

Mirabilis discusses role of deployment level simulation to

optimize reliability delivered by SSD controller design tweaks

Editor:-

August 16, 2015 - "A diligent system designer can extend the life of an SSD

by upto 60% by proper control of over-provisioning, thus reducing TCO"

says Deepak

Shankar, Mirabilis

Design in his recent paper

Extending

the Lifetime of SSD Controllers (pdf) which discusses the role of

application and deployment level simulations to explore the impact of

changing brews in controller

architectural coctails.

See also:-

SSD

overprovisioning articles 2003 to 2015

Altera launches adaptive endurance controller for PCIe SSD market

Editor:-

June 23, 2015 -Altera

today

announced

availability of a new flash controller reference design for the

NVMe PCIe SSD market

which uses adaptive

R/W endurance.

The

Arria

10 SoC (pdf) which includes among other things an integrated dual-core ARM

processor uses flash IP from

Mobiveil and NAND

optimization software from

NVMdurance to

simplify the design of gen 3 PCIe SSDs having 7x better endurance than

classical non adaptive designs.

Editor's comments:- Since the

market criticality of adaptive DSP flash controller techniques for enterprise

SSDs began to emerge in 2011 and then clarified in a big way in 2012 - it has

become an essential capability for most product lines. This standard product

from Altera fills a much needed gap in their offerings.

|

|

The SSD controller page in

past years.

Readers doing research on the evolution of the SSD

controller market have tiold me they find it useful to see archived versions of

this news page.

The internet archive lets you see the SSD

controller page from

2009

to the present day.

Other options are

archived storage

and SSD news from 2000.

Or put the words "SSD controller"

into the site search box below. (It's all here on this site if it was important

in the SSD market.) |

|

|

| |

| .......................................................................................................................... |

|

|

| ......................................................................................................................... | |

| ... |

|

| firming up the reference

design | |

|

. |

|

| If you could go back in

time and take with you a factory full of modern memory chips and SSDs

(along with backwards compatible adapters) what real impact would that have?

|

| are we ready for

infinitely faster RAM?

| | |

|

. |

|

|

|

. |

|

SSD testing /

reliability /

CPUs in

the post modern SSD era |

|

. |

|

In the current state of the

SSD market it's possible for systems companies to use array level software to

deliver efficiencies and reliabilities which are as good and sometimes much

better than any controller company can deliver in the best solo SSD while the

array company uses me-too or not very impressive controllers in each SSD.

The

consequences are that the SSD controller market will fragment into:-

- lowest cost for standard functions, and

- ability to customize

(and collaborate) by software

- outstanding capability for high value markets in a solo SSD

The

array

market will become a can't sell zone for any controller company which tries

to over-deliver unwanted features (and

fool's gold value)

in its solo SSD nodes.

And at the same time well see systems

companies doing more customization of controllers.

That means controller companies which do introduce standout features

will have to figure out

where they stand

with respect to future standardization and customization. |

StorageSearch.com

editor in

conversation (August

2016)

custom

matters in SSDs

SSD

market changes in 2016

controllernomics - is

that even a real word?

| | |

|

. |

|

|

|

. |

|

|

|

. |

|

|

|

Renice ran the banner ad shown

below in 2012 on StorageSearch.com to promote awareness of its USB 3 flash

controller.

The SSD market's first web ads for SSD controllers began

here in 2011.

That was for SandForce.

The SandForce

controller ads continued through the ownership by LSI and subsequently

Seagate right upto the first quarter of 2017.

See the 2010 article

Imprinting the brain

of the SSD for the story of how the merchant SSD controller market suddenly

became important and how SandForce helped to make that awareness become

mainstream.

The first SSD ads for enterprise SSDs started here in 2000. |

|

. |

|

|

|

above - an SSD controller ad circa 2012

. |

|

| Surviving SSD

sudden power loss |

Why should you care

what happens in an SSD when the power goes down?

This important design

feature - which barely rates a mention in most SSD datasheets and press releases

- has a strong impact on

SSD data integrity

and operational

reliability.

This article will help you understand why some

SSDs which (work perfectly well in one type of application) might fail in

others... even when the changes in the operational environment appear to be

negligible. |

|

| | |

|

. |

|

|

|

. |

|

|

|

. |

|

. |

|

|

|

. |

|

| |